Product Summary

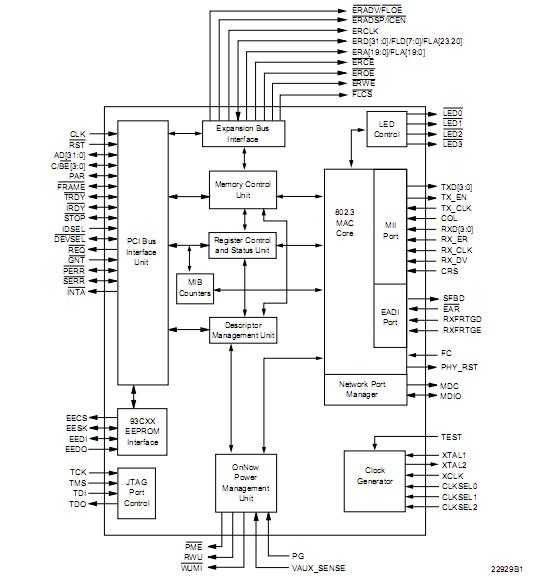

The AM79C976KF is a highly-integrated 32-bit full-duplex, 10/100-Megabit per second (Mbps) Ethernet controller solution, designed to address highperformance system application requirements. It is a flexible bus mastering device that can be used in any application, including network-ready PCs and bridge/router designs. The bus master architecture provides high data throughput and low CPU and system bus utilization. The AM79C976KF controller is fabricated with advanced low-power 3.3-V CMOS process to provide low operating current for power sensitive applications. The AM79C976KF is ideally suited for Net PC, motherboard, network interface card(NIC), and embedded designs. It is available in a 208-pin Plastic Quad Flat Pack (PQFP) package.

Parametrics

AM79C976KF absolute maximum ratings: (1)Storage Temperature:-65℃ to +150℃; (2)Ambient Temperature:-65℃ to +70℃; (3)Supply voltage with respect to VSSB, VSS:–0.3V to 3.63V.

Features

AM79C976KF features: (1)32-bit glueless PCI host interface; (2)Supports PCI clock frequency from DC to 33 MHz independent of network clock; (3)Supports network operation with PCI clock from 15 MHz to 33 MHz; (4)High performance bus mastering architecture with integrated Direct Memory Access (DMA) Buffer Management Unit for low CPU and bus utilization; (5)PCI specification revision 2.2 compliant; (6)Supports PCI Subsystem/Subvendor ID/Vendor ID programming through the EEPROM interface; (7)Supports both PCI 3.3-V and 5.0-V signaling environments; (8)Plug and Play compatible; (9)Uses advanced PCI commands (MWI, MRL, MRM); (10)Optionally supports PCI bursts aligned to cache line boundaries; (11)Supports big endian and little endian byte alignments ; (12)Implements optional PCI power management event (PME) pin; (13)Supports 40-bit addressing (using PCI Dual Address Cycles); (14)Automatically inserts, deletes, or modifies VLAN tag; (15)Optionally filters untagged frames; (16)Programmable PHY reset output pin capable of resetting external PHY without needing buffering ; (17)Integrated oscillator circuit is controlled by external crystal; (18)Extensive programmable LED status support ; (19)Supports up to 16 Mbyte optional Boot PROM or Flash for diskless node application; (20)Look-Ahead Packet Processing (LAPP) data handling technique reduces system overhead by allowing protocol analysis to begin before the end of a receive frame.

Diagrams

|

Am79213 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

Am79231 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

Am79514 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

Am79533I |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

Am79534 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

Am79535 |

Other |

|

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))