Product Summary

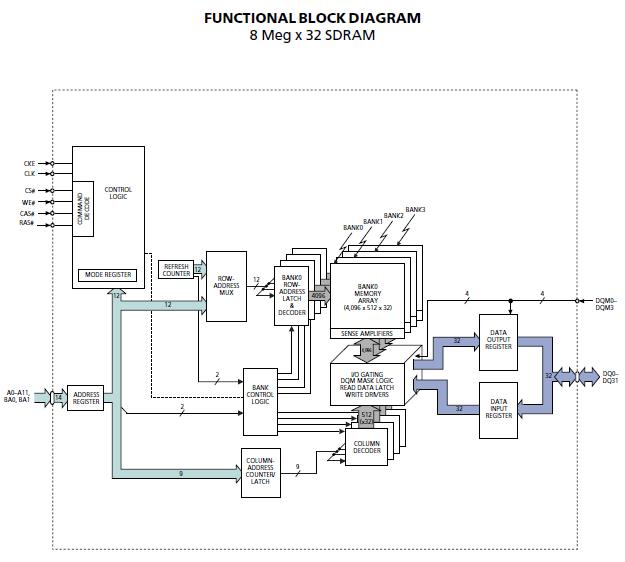

The MT48LC8M32B2P-6 256Mb SDRAM is a high-speed CMOS, dynamic random-access memory containing 268,435,456-bits. It is internally configured as a quad-bank DRAM with a synchronous interface (all signals are registered on the positive edge of the clock signal, CLK). Each of the 67,108,864-bit banks of MT48LC8M32B2P-6 is organized as 4,096 rows by 512 columns by 32 bits.

CCX102 HYS72D32300HU-6-C MT28F800B1-10 SP08-R

CCX187 HYSF6404D MT29C1G12MAUNAJC-6 SP093

CCX413-2 HYSTB-1003 MT29C4G48MAZAPZKD-5IT SP1/8NN25

CCY7C142 HYUF611CL MT29F32G08CBAAAWP SP100006CFU

CD034AP HZ11A2-E MT3205AE SP1010LN

CD0402-T05LC HZ11A3-Q MT3211B0 SP101A1123HBL

CD0402-T36C HZ11B1TD MT326230 SP101A1123HBLGN

CD0603-Z7V5 HZ11C2-Q MT3330C4 SP102520CFU

CD1005 HZ11C2TA MT3371BC SP105975CFU

CD1013 HZ1206E601R-10 MT34013D SP1060S

CD1018CP HZ12A1TA MT3407VC01L SP110UYG

CD1019CP HZ12A2-E MT36HTF1G72FZ-667C1D4 SP1122NA

CD101BCN HZ12A3/ MT36HTF51272FDZ-80EH1N8 SP-1184

CD1031CP HZ15-1-E MT3725VB SP1200

CD10RM05K HZ152L MT3S06S SP1204C-3C

CD1191C HZ16-1 MT3S07TAD SP122J

CD1274V2 HZ16A3 MT3S07U SP125-470M

CD12DR-BL HZ17324A MT3S08FS SP12586

CD137B1H HZ181TA MT3S107T SP12K21B

CD1404CB HZ18-1TA-Q MT-405-Z SP-12SH

CD1585BC HZ18-2LTA-E MT4067-10IT SP1359

CD15CD020D03F HZ18-2TA MT4067-150 SP139976

CD15ED280DO3 HZ18CPTK MT4067C-10/883C SP1408

CD15ED330JO3F HZ20-1LTA-E MT4102 SP1450BB

CD15FD121F03 HZ20-2RE MT41J128M16HA-15EIT SP1491ECN-L

CD-15FD221J03 HZ20-3-E MT4302A-HR SP14N002J

CD1619BS HZ220R/B MT4311BE SP14N003

Parametrics

MT48LC8M32B2P-6 absolute maximum ratings: (1)Voltage on VDD, VDDQ Supply Relative to VSS: -1V to +4.6V; (2)Voltage on Inputs, NC or I/O Pins Relative to VSS: -1V to +4.6V; (3)Operating Temperature, TA: 0℃ to +70℃; (4)Storage Temperature (plastic): -55℃ to +150℃; (5)Power Dissipation: 1W; (6)Operating Temperature, TA (IT): -40℃ to +85℃.

Features

MT48LC8M32B2P-6 features: (1)PC100 functionality; (2)Fully synchronous; all signals registered on positive edge of system clock; (3)Internal pipelined operation; column address can be changed every clock cycle; (4)Internal banks for hiding row access/precharge; (5)Programmable burst lengths: 1, 2, 4, 8, or full page; (6)Auto Precharge, includes CONCURRENT AUTO PRECHARGE, and Auto Refresh Modes; (7)Self Refresh Mode; (8)64ms, 4,096-cycle refresh (15.6μs/row); (9)LVTTL-compatible inputs and outputs; (10)Single +3.3V ±0.3V power supply; (11)Supports CAS latency of 1, 2, and 3.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||

|---|---|---|---|---|---|---|---|---|---|---|

|

MT48LC8M32B2P-6 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

MT48LC8M32B2P-6 TR |

|

IC SDRAM 256MBIT 166MHZ 86TSOP |

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))